# Dogo Rangsang Research JournalUGC Care Group I JournalISSN : 2347-7180Vol-09 Issue-01 No. 01 : 2022Leakage Power Reduction Technique for Network Routing Using Memristor based TCAM

**N.SUBHARATHNA** PG Scholar, Department of Electronics and Communication Engineering, Nandha Engineering College.

**K.SHARMILEE** Professor, Department of Electronics and Communication Engineering, Nandha Engineering College.

Abstract: A memristor is associate electrical half that limits or regulates the flow of electrical current in associate extremely circuit and remembers the number of charge that has previously flowed through it. Memristors unit of measurement non-volatile, meaning that they preserve memory whereas not power. The definition of memristor has been broadened to include any kind of non-volatile memory that is supported resistance amendment, which will increase the flow of current in one direction and reduces the flow of current at intervals the opposite means. Ternary Content Addressable Memory (TCAM) cell that employs memristors as storage element. The TCAM cell wants two memristors nonparallel to perform the quality memory operations (read and write) further more as a result of the search and matching operations for TCAM; this memory cell is analyzed with connexion fully completely different choices (such as memristance vary and voltage threshold) of the memristors to technique fast and expeditiously the ternary information. Comparison with completely different memristor-based CAMs furthermore as CMOS-based TCAMs shows that the projected cell offers vital blessings in terms of power dissipation, reduced semiconductor count and search/match

operation performance.

#### I. Introduction:

MOBILE communication plays a really necessary role in trendy life. With the progress of telecommunication technology, an oversized range of applications area unit designed, like video stream, online game, navigation, etc., However, this feature would induce significant run power since an oversized range of transistors area unit used. this means that the TCAM would consume a lot of power and pay a lot of time to recover these knowledge. A memristor (memory resistor) could be a non-linear two-terminal electrical part relating charge and magnetic flux linkage. fantastic growth within the range of net users and also the increasing quality of information measure hungry real time applications have resulted in an exceedingly demand for very high-speed networks. the web could be a mesh of routers and switches, that method knowledge packets and forwards them toward their destinations. every packet contains a header and a payload. The header contains info like a supply address, a destination address, the info length, a sequence range and also the knowledge form of the packet.

A network switch transfers associate degree

incoming knowledge packet to associate degree output port supported the knowledge within the header of the packet. every router maintains a routing table and forwards incoming packets supported the knowledge keep within the routing table. Router additionally communicate with each other to update their routing tables. Ternary Content Addressable Memory (TCAMs) area unit wide utilized in networking circuits for address classification and packet filtering. superior network routers need quick and high capability TCAMs for improved look-up performance of routing tables. However, the fabrication and style of TCAM chips with an oversized storage capability have encountered substantial issues in CMOS. a big drawback is expounded to the look itself; ternary logic needs extra provide voltages if enforced by CMOS electronic equipment. while not the utilization of extra power rails, the dimensions of the ternary memory cell is increased because of the employment of 2 binary cells (i.e. a minimum of twelve transistors, or 12T) and extra transistors for the connected comparison circuit. whereas a TCAM cell with a reduced semiconductor count has been reported, stability issues area unit encountered if this cell is employed in giant storage chips. Also, a TCAM consumes vital power because of its operations like a totally parallel search throughout the memory array.

The memory cells in a very TCAM will store 3 states (i.e., '1', '0', '2'). the extra state '2' is additionally mentioned because the "mask" or "don't care" state; it's used for matching to either a '0' or '1' within the input search knowledge method. The search operations of a TCAM area unit performed by comparison in parallel the input (searched) knowledge against the complete list of entries keep in memory. A TCAM is best fitted to network applications like a Network Intrusion Prevention **Page | 525**

#### UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

System (NIPS), LAN address search, knowledge compression, user privileges and routers.

This paper proposes a brand new hybrid style for a Ternary CAM (TCAM) that utilizes memristors. This memory cell is analyzed with regard to totally different options (such as memristance vary and voltage threshold) of the memristors to method quick and expeditiously ternary knowledge. Comparison with alternative memristor-based CAMs in addition as CMOS-based TCAMs shows that the planned cell offers vital benefits in terms of power dissipation, reduced semiconductor count and search/match operation performance.

#### **II. Literature Survey:**

"Low leakage mask vertical control TCAM for network router"

Ternary content available memory (TCAM) is often utilized in the network routing since it will perform the parallel science operation. However, the ability consumption of the normal router must be thought of too. significantly, the escape power can increase because the technology feature size shrinks. A TCAM design with mask vertical management (MVC) technique is projected to scale back the escape power of network router. within the forwarding table, supported the science hold on so as of prefix length, the MVC technique will shut down the unessential power provide to scale back the escape power. The TCAM with the MVC technique was simulated by victimization the TSMC ninety nm method. Compared with the normal TCAM design, the MVC theme can do regarding twenty first escape power reduction.

# "Low leakage TCAM for IP lookup using two-side self-gating"

Ternary content-addressable memory (TCAM) may be a standard hardware device for Copyright @ 2022 Authors

quick routing search and a pretty answer for applications like packet forwarding and classification. However, the high value and power consumption area unit limiting its quality and flexibility. an occasional run power TCAM design that uses two-side self power gating technique is projected to scale back the run power dissipation of the mask SRAM cells. The TCAM mask cells area unit divided into many segments, and also the mask bits of 1 phase area unit constant aside from the boundary phase. The boundary phase is activated and also the others area unit disabled so the run power may be reduced. The experimental results show that average twenty sixth run power may be reduced by exploitation UMC ninety nm CMOS method with one.0 V provide voltage compared with the normal TCAM design.

#### **III. Review of Memristors:**

A memristor may be a non-linear two-terminal electrical part relating charge and magnetic flux linkage. it had been postulated in 1971 by Leon Chua, finishing a theoretical quartet of elementary electrical parts that includes additionally the electrical device, capacitance and inductance. the link between the flux and therefore the charge of a memristor is given by,

$$d\phi = M * dq \tag{1}$$

where M is that the memristance or memristor price (in  $\Omega$ ), Ø is that the flux through the magnetic flux, and letter of the alphabet is that the charge, i.e., this moving through the memristor is proportional to the flux of the magnetic flux that flows through the fabric. Therefore, the magnetic flux between the terminals may be a perform of the quantity of charge (i.e., q) that flows through the device. (1) is admire V=MI, wherever V and that i square measure voltage and current across the memristor, severally. A

#### UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

memristor operates as a resistor whose price depends on this or voltage across it, i.e., if there's a positive voltage across the memristor, its memristance can reduces to a tiny low price (given by  $R_{ON}$ ); if there's a negative voltage across the memristor, its memristance will increase up to a high price (given by R<sub>OFF</sub>). Hereafter, the memristor is taken into account as a shift resistance device, the speed of modification for the memristance is typically linear, provided its price isn't shut to the acute values (RON and ROFF). If the memristance price is getting ready to the acute values (RON or ROFF), non- dimensionality is probably going to occur for its rate of modification. As physical implementation of a memristor, has made-up a tool supported a titania film sandwiched between 2 noble metal electrodes. The memristor consists of 2 components (or regions), the doped region and therefore the undoped region. The widths of the doped region (w) and therefore the undoped region (L - w) modification betting on the direction of this or voltage across it. Let be the resistance for fully a totally a very doped memristor and ROFF be the resistance for a completely undoped memristor; thus, this voltage relationship of the memristor is given as follows,

$$\boldsymbol{v}(t) = \left\{ R_{0N} \frac{\omega(t)}{L} + R_{0FF} \left( 1 - \frac{w(t)}{L} \right) \right\} i(t)$$

(2)

where w(t) is that the breadth of the doped region, and L is that the TiO2 thickness.

### IV. Memristor based TCAM Cell:

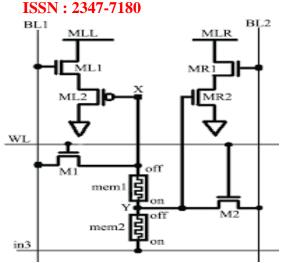

Due to its non-volatile characteristic, the memristor will be used as a memory device. The 3 states of the TCAM square measure outlined mistreatment two memristors as follows.

Dogo Rangsang Research Journal

Figure 1. proposed TCAM design using memristors

- For state '0', each memristors should be totally biased to the R<sub>OFF</sub> state. Total resistance of the memory cell is 2R<sub>OFF</sub>.

- In state '1', each memristors should be within the state. So, the whole resistance of the memory cell is 2R<sub>ON</sub> i.e., a really low price compared with the resistance in state '0'.

- For state '2' (i.e., the don't care state), • one memristor should be within the state. whereas the opposite memristor should be within the ROFF state. Therefore, the whole resistance of the TCAM cell in state '2' is R<sub>OFF</sub>. because the price of R<sub>OFF</sub> is considerably larger than the whole resistance of state '2' TCAM is about up to R<sub>OFF</sub>, i.e., a price within the middle of the vary between those for state '0' and state '1'. The write and matching operations of the planned TCAM cell square measure bestowed. The write and matching operations of the proposed TCAM cell are presented.

- A) Write Operation:

# UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

The planned TCAM cell has 2 memristors connected nonparallel. The write operation consists of 2 distinct components. In Figure one the write line (WL) is high throughout the write operation, knowledge is provided through bit line one (BL1), bit line two (BL2) and input three line (in3) as follows.

1) Write '0':

To write a '0', each memristors got to be within the  $R_{OFF}$  state. Then, WL should be enabled (ON or high), whereas BL1 and in3 square measure low and high, severally. throughout the primary a part of the write operation, BL2 is low and thus mem2 is within the  $R_{OFF}$  state. within the second a part of the write operation, BL2 is high for mem1 to be within the  $R_{OFF}$  state, thus at completion of this method, each memristors square measure within the  $R_{OFF}$  state.

2) Write '1':

For writing a '1', each memristors should be within the state. this is often just like the write '0' operation; thus, WL is high. BL1 is additionally high, whereas in3 is low. BL2 is low throughout the primary a part of the write operation, so mem1 is within the state. throughout the second a part of the write operation, BL2 is high such mem2 is within the state conjointly. Hence, each memristors square measure within the state.

3) Write '2':

In this case, one memristor should be within the state whereas the opposite memristor should be within the ROFF state. So, the write line is high, while BL1, BL2, in3 square measure low, high and low severally. Therefore, mem1 is within the R<sub>OFF</sub> state and mem2 is within the state.

B) Search Operation:

The search operation during a TCAM cell checks whether or not there's a match between the searched (provided as input) and hold on knowledge. 2 match lines (MLL and MLR) square measure used (Figure 1); these 2 lines square measure shown to raised understand the operations of the planned TCAM cell and therefore the discharge process; in apply these 2 lines are often combined into one line. The search operation starts by pre-charging the voltage on MLL and MLR to high. Then, the searched knowledge is input through BL1 and BL2. A high voltage (VDD) is applied from in3 to each mem1 and mem2 to check the knowledge information hold on within the TCAM cell with the searched data. If the knowledge information hold on within the TCAM cell is equal (matched) to the searched data, the match line is discharged. Else (no match), its voltage is unbroken unreduced.

1) Search '0':

The MLs should be pre-charged to VDD before beginning the search operation. For the search '0' operation, BL1 and BL2 square measure high and low severally, i.e., ML1 is ON and MR1 is OFF. Then, the information input is placed through in3 to envision the state of the TCAM cell. In Figure one, every memristor is totally biased to its needed state ( $R_{ON}$  or  $R_{OFF}$ ). Once a memristor is within the West Chadic state, the free fall across it's a awfully low worth (especially in comparison with the ROFF state). the subsequent cases are often distinguished for the search '0' operation.

If the TCAM cell is in state '0', each memristors should be within the R<sub>OFF</sub> state, V<sub>X</sub> and V<sub>Y</sub> square measure terribly low (i.e., ML2 is ON and MR2 is OFF). For the search '0' operation, ML1 is ON and MR1 is OFF, an immediate path

# UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

exists from MLL to GND and MLL is discharged.

- For state '2', mem1 should be within the ROFF state and mem2 should be within the West Chadic state, thus V<sub>X</sub> and V<sub>Y</sub> square measure low and high severally. Then, ML2 and MR2 square measure ON, an immediate path from V<sub>DD</sub> to GND exists via ML1 and ML2; MLL is discharged.

- For state '1', each memristors should be within the West Chadic state; thus, throughout the search operation, V<sub>X</sub> and V<sub>Y</sub> square measure high. Then, ML2 and MR2 square measure OFF and ON severally. As MR1 is OFF, there's no direct path from V<sub>DD</sub> to GND; MLL and MLR retain their values, as results of the no-match.

- 1) Search '1':

For the search '1' operation, BL1 and BL2 square measure low and high severally. So, ML1 is OFF and MR1 is ON. counting on the information hold on within the cell, the match line voltages of the planned cell square measure as follows.

- If the TCAM cell is in state '0', each memristors square measure within the R<sub>OFF</sub> state; so, V<sub>X</sub> and V<sub>Y</sub> square measure terribly low (ML2 is ON and MR2 is OFF). there's no direct path from VDD to GND (i.e., no match is found).

- If the TCAM cell is in state '1' or '2', mem2 is within the West Chadic state and  $V_Y$  is high. Therefore, as MR2 is ON, there's an immediate path from MLR to GND, so inflicting MLR to discharge.3)

**Copyright @ 2022 Authors**

2) Search '2':

For the search '2' operation, the result's continually a match as a result of it's the "don't care" state. So, each BL1 and BL2 square measure high and ML1 and MR2 square measure ON. an immediate path exists from the MLL and MLR to GND, so continually leading to a match.

#### V. Simulation Results:

The performance analysis of the TCAM cell of Figure 1 is bestowed victimization at 32nm CMOS technology. The model is used for the memristor with a memristance vary of  $100\Omega$ -19k $\Omega$ . A. Write Time: The write time is that the time for the memristor is outlined because the memristor time for memristor to be within the desired state. By setting the voltage across the memristor to a relentless price (equal to zero.9 V), it's been found that the time for totally biasing one memristor to its state is or so two hundred ns. to totally charge each memristors, the write time may be found as follows (under the belief that the fall across money supply or money supply is given by zero.45V). B. Search Operation: The search operation for the TCAM cell of Figure one is simulated as, the match lines MLL and MLR area unit separate to indicate the results of the match operation on either side of the TCAM cell. The match/mismatch outcome of TCAM cell is generated by combining these 2 lines along into one line (i.e. the output of associate degree gate with MLL and MLR as inputs).

Table 1. Comparison between transistor size and write time for a memristor range of  $100\Omega$ -19k $\Omega$

| Technology | V <sub>DD</sub> (V) | Write    | Read     |

|------------|---------------------|----------|----------|

|            |                     | Time(ns) | Time(ns) |

| 32nm       | 1                   | 270      | 6.08     |

|            | 1.1                 | 210      | 6.28     |

| 45nm       | 1                   | 300      | 6.70     |

# UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

|  | 1.1 | 230 | 7.20 |  |

|--|-----|-----|------|--|

|  |     |     |      |  |

The simulation ends up in Table one show that the projected TCAM cell may be enforced at 32nm with a coffee write time. additionally correct operation is achieved, as a result of its search time is quicker than the time needed for reaching the brink level of the memristor. the speed of modification of the memristors is extremely low if provide the availability the provision voltage is reduced at low scaling (the supply voltage of 32nm is a smaller amount than for 45nm). This feature is additionally advantageous for power dissipation as at 32nm, less power is additionally needed.

# VI. Conclusion:

This paper has conferred a Ternary Content available Memory (TCAM) cell style by victimization memristors as storage part. Since ternary logic is employed, 2 memristors connected nonparallel area unit utilized to represent every state of the TCAM. The planned TCAM has been extensively analyzed by considering memristance vary, threshold voltage, semiconductor unit size and provide voltage with relation to memory operations like write and search. The planned memory cell operates robustly and style issues involving memristance vary and threshold choice are analyzed to realize quick operation for writing and looking at 32nm feature size. Simulation results have confirmed that the planned style offers vital performance enhancements compared with different CAM styles utilizing memristors.

# **VII. References:**

[1] W. Zhang, L. Li, and J. Hu, "Design techniques of P-type CMOS circuits for gate-leakage reduction in deep sub-micron ICs," in Proc. IEEE 52<sup>nd</sup> Int.

Midwest Symp. Circuits Syst. (MWSCAS), Aug. 2009, pp. 551–554. BGP Routing Table Analysis Reports. Accessed: Nov. 15, 2019.

- [2] Li, C. et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nat. Communication 9, 2385 2018.

- [3] Y.C. Cheng, J.-H. Chen, T.-C. Wu, and Y.-J. Chang, "Low leakage mask vertical control TCAM for network router," in Proc. IEEE Asia– Pac. Conf. Circuits Syst. (APCCAS), Oct. 2016, pp. 469–472.

- [4] P.Junsangsri, F. Lombardi and Jie Han, "A memristor-based TCAM (Ternary Content Addressable Memory) cell", proc. of International Symposium on Nanoscale Architectures (NANOARCH), pp. 1-6, 8–10 July 2014.

- [5] Le Zheng, Sangho Shin and Kang Sung-Mo Steve,

"Memristor-based ternary content addressable memory (MTCAM) for data-intensive computing", Semiconductor Science and Technology (IOP Science), vol. 29, no. 10, pp. 104010, 2014.

- [6] S. Tabassum, F. Parveen and A. B. M. Harun-ur Rashid, "Low power high speed Ternary Content Addressable Memory design using 8 MOSFETs and 4 memristors-hybrid structure", International Conference on Electrical and Computer Engineering (ICECE), pp. 168-171, Dec. 2014.

- [7] Y.-J. Chang, K.-L. Tsai, and H.-J. Tsai, "Low leakage TCAM for IP lookup using two-side selfgating," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 6, pp. 1478–1486, Jun. 2013.

- [8] Zhang Lu, Chen Zhijie, J. Joshua Yang, Bryant Wysocki, Nathan McDonald and Yiran Chen, " A compact modeling of TiO 2 TiO 2-x memristor ", Appl. Phys. Lett., vol. 102, pp. 153-503, 2013.

# UGC Care Group I Journal Vol-09 Issue-01 No. 01 : 2022

- [9] Mishra Nilesh and M Kittur Harish, "4 -Transistors of Dynamic Memristor based TCAM", International Journal of Engineering Research and Applications (IJERA), vol. 2, no. 3, pp. 2520-2524, May-Jun 2012.

- [10] K. J. Kuhn, "Considerations for ultimate CMOS scaling", IEEE Trans. Electron Devices, vol. 59, pp. 1813-1828, Jul 2012.

- [11] K.Eshraghian, K.R.Cho, O.Kavehei, S. K Kang, D, Abbott, S. M. Steve Kang, "Memristor MOS Content Addressable Memory (MCAM): Hybrid Architecture for Future High Performance Search Engines" IEEE Transactions on VLSI Systems, vol. 19, no. 8, pp. 1407--1417, 2011.

- T.Prodromakis, Boon Pin Peh, C.Papavassiliou and C.Toumazou, "A Versatile Memristor Model With Nonlinear Dopant Kinetics", IEEE Transactions on Electron Devices, vol. 58, no. 9, pp. 3099-3105, Sept. 2011.

- [13] A.Rak, G.Cserey, "Macromodeling of the Memristor in SPICE," IEEE Trans. Computeraided design of integrated circuits and systems, vol. 29, no. 4, pp. 632--636, Apr 2010.

- [14] Y.-J. Chang, "Using the dynamic power source technique to reduce TCAM leakage power," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 11, pp. 888–892, Nov. 2010.

- [15] D. Batas and H. Fiedler, "A memristor spice implementation and a new approach for magnetic flux controlled memristor modeling," Nanotechnology, IEEE Transactions on, vol. PP, no. 99, pp. 1--1, 2009.

- [16] Z. Biolek, D. Biolek, V. Biolova, "SPICE model of memristor with nonlinear dopant drift," Radio engineering, vol. 18, no. 2, pt. 2, pp. 210--214, 2009.